집적 회로

집적 회로(集積回路, 영어: Integrated Circuit) 또는 모놀리식 집적 회로, IC칩, 컴퓨터 칩, 마이크로칩, IC는 반도체로 만든 전자회로의 집합을 말한다. 집적 회로는 여러 독립된 요소를 집적해서 하나의 칩으로 만든 것인데 각각의 트랜지스터 칩을 이용해서 회로로 만들 때보다 훨씬 작게 만들 수 있다. 집적 회로는 손톱 수준의 크기에 수십억 개의 트랜지스터나 다른 전자부품이 들어갈 수 있을 정도로 조밀하게 만들 수 있다. 기술이 발전할수록 회로선폭은 점점 더 세밀해진다. 2008년에는 100나노미터 미만으로 떨어졌고[1], 지금은 수십 나노미터다[2].

반도체 소자가 진공관처럼 증폭기 및 스위치 역할을 할 수 있다는 것이 밝혀지고, 반도체 제작 기술이 발달하면서 집적 회로를 만들 수 있게 되었다. 매우 많은 수의 작은 트랜지스터를 작은 칩에 합치는 것은 전자 부품을 이용하여 손으로 회로를 조립하는 것을 넘어서는 굉장한 발전이었다. 집적 회로의 대량생산 능력, 신뢰성, 회로 설계에 대한 빌딩블록 방식 접근은 이산 트랜지스터를 이용하던 산업이 빠르게 집적 회로를 적용할 수 있도록 하였다.

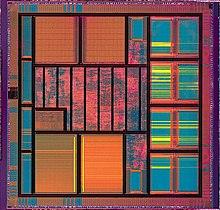

집적 회로는 이산회로에 비교해서 비용과 성능이라는 두 가지 주요한 장점이 있다. 한 번에 하나의 트랜지스터를 조립하는 방식과는 달리 사진석판술을 이용하여 모든 부품을 한꺼번에 찍어내기 때문에 비용이 낮아진다. 또한 크기가 작고 부품들이 조밀하게 설계되어 동작 속도가 빨라지고, 전력 소모는 줄어들게 된다. 2012년에 전형적인 집적 회로의 크기는 수 제곱 밀리미터에서 약 450㎟였고, 제곱 밀리미터당 약 900만 개의 트랜지스터가 들어있었다.

집적 회로는 전자공학에 혁명을 일으켰고 오늘날 거의 모든 전자장비에 사용된다. 현대사회에서 필수불가결한 컴퓨터, 휴대폰 그리고 다른 모든 가전기기들은 싼 가격의 집적 회로 덕분에 가능한 것들이다.

정의

편집집적 회로는 다음과 같이 정의된다:[3]

발명

편집초기 집적 회로의 개발은 독일의 공학자인 베르너 야코비(Werner Jacobi)[6]가 집적 회로와 유사한 반도체 증폭 기기에 대한 특허권[7]을 얻은 1949년으로 거슬러 올라간다. 특허권을 얻은 반도체 증폭기는 공통기판 위에 5개의 트랜지스터를 포함했고 3단 증폭기 배열로 구성되어 있었다. 베르너 야코비는 그의 특허를 응용하는 예로 작고 싼 보청기를 제시했다. 그의 특허에 대한 직접적인 상업적 사용은 알려진 바가 없다.

집적 회로의 아이디어는 영국 국방성의 왕립 레이다 시설에서 일하고 있던 레이다 과학자인 제프리 더머(1909-2002)가 생각해냈다. 더머는 1952년 5월 7일 워싱턴주에서 열린 한 심포지엄에서 그 아이디어를 발표했다.[8]. 그는 많은 심포지엄에서 그의 아이디어를 알렸지만 1956년 회로를 실제로 구현하려는 그의 시도는 실패했다.

1958년에 제안된 집적 회로에 다가가는 선구적인 아이디어는 각각 별개의 축소시킨 소자를 포함한 작은 세라믹판, 또는 웨이퍼를 만드는 것이었다. 소자들은 그 후에 2차원이나 3차원 적인 압축된 그리드에 통합되고 선으로 연결된다. 당시엔 매우 유망해보였던 이 아이디어는 잭 킬비가 미 육군에게 제안한 것이었고, 미 육군의 초소형 전자제품 개발 계획인 마이크로모듈 프로그램으로 이어졌다[9]. 하지만 프로젝트를 진행하던 중 킬비는 새롭고 혁신적인 집적 회로를 생각해냈다. 콘덴서와 저항기를 트랜지스터 제조에 사용된 것과 동일한 반도체 물질로 된 기판위에다 제조, 집적시키는 것이었다.

킬비는 1958년 텍사스 인스트루먼트에 입사한 뒤 그해 7월에 집적 회로에 관한 그의 첫 아이디어를 기록으로 남겼고, 1958년 12월 12일에 그의 상사에게 처음으로 작동할 수 있는 집적 회로를 보여줄 수 있었다[10]. 1959년 2월 6일, 그의 특허 신청서에서 킬비는 그의 새로운 기기를 "몸체는 반도체이고...모든 소자들은 전자회로 안에 완벽히 집적되어있다"라고 묘사했다[11]. 그의 새로운 발명에 대한 첫 번째 고객은 미 공군이었다[12].

킬비는 집적 회로의 발명에 대한 공로로 1982년에는 미국 발명가 명예의 전당에 오르고 2000년에는 노벨 물리학상을 받았다[13]

킬비가 집적 회로를 생각해내고 반년 뒤, 페어차일드 반도체의 로버트 노이스는 킬비가 풀지 못한 많은 실용적 문제들을 푼 집적회로 아이디어를 생각해냈다. 노이스가 생각해낸 집적 회로는 게르마늄으로 이루어진 킬비의 집적 회로와는 달리 실리콘으로 이루어져 있었다. 노이스는 p-n 접합 절연의 아이디어를 스프라그 일렉트릭의 커트 레호벡에게서 얻었다고 밝혔는데[14], 이 절연 덕분에 한 실리콘 위에 있는 트랜지스터가 독립적으로 동작할 수 있게 되었다.

페어차일드 반도체는 또한 현대의 모든 CMOS(Complementary Metal–Oxide–Semiconductor,상보형 금속 산화 반도체) 컴퓨터 칩의 기본이 되는, 셀프 얼라인 게이트를 이용한 첫 번째 실리콘 게이트 집적 회로가 만들어진 곳이다. 그 기술은 1968년 이탈리아의 물리학자인 페데리코 파긴에 의해 개발되었고, 그는 후에 첫 번째 단일 칩인 CPU(인텔4004)를 개발하기 위해 인텔에 합류했다. 그 공로로 그는 2010년 전미 기술메달을 받았다.

세대

편집초기 집적 회로는 트랜지스터 몇 개만 포함되었고, 설계 과정도 상대적으로 단순했다. 제조 분야 또한 오늘날의 기준으로는 꽤 미흡했다. 기술이 발달하면서 수십억 개의[15] 트랜지스터가 하나의 칩에 들어갈 수 있었고 새로운 설계 방법이 등장했다. 집적회로는 포함된 트랜지스터의 수에 따라 분류할 수 있다[16].

SSI, MSI, LSI

편집처음 개발된 집적 회로는 트랜지스터 몇 개만 들어가 있었다. 소규모 집적이라는 뜻의 SSI(small-scale integration)라고 불리는 디지털 회로는 수십 개의 트랜지스터만을 포함할 수 있었고 소수의 논리게이트를 구현했다. 예를 들어 초기 리니어 IC는 2개의 트랜지스터밖에 없었다. 대규모 집적이라는 말은 IBM의 연구원인 롤프 란다우어가 이론적인 개념을 설명할 때 처음 사용했고 그것에서 SSI나 MSI, VLSI, ULSI가 유래했다.

집적 회로의 다음 단계의 발전은 1960년대 후반, 중간 규모의 집적이라는 뜻의 MSI(Middle Scale Integration)라고 불리는 한 칩에 수백 개의 트랜지스터를 포함하는 기기가 소개되면서 일어났다. MSI는 100~1000개의 트랜지스터를 포함하고, 좀더 복잡한 기능을 수행하는 인코더(encoder), 디코더(decoder), 카운터(counter), 레지스터(register), 멀티플렉서(multiplexer) 및 디멀티플렉서(demultiplexer), 소형 기억 장치 등의 기능을 포함하는 부류다. MSI소자는 SSI소자보다 생산하는데 비용이 조금 더 들지만, 작은 회로기판과 적은 조립 작업으로 더 복잡한 시스템을 구현할 수 있기 때문에 경제적으로 매력적이었다.

1970년대 중반, 한 칩에 수만 개의 트랜지스터를 포함하는 LSI가 MSI와 같은 이유로 개발되었다. LSI는 메모리 등과 같이 하나의 칩에 1,000~10,000개에 이르는 등가 게이트를 포함하는 부류이다.

1Kb 램이나 계산기 칩, 세계 최초의 마이크로프로세서 같은 1970년대 꽤 많이 생산되었던 집적 회로들은 4천개 이하의 트랜지스터를 포함했다. 만개에 가까운 트랜지스터를 포함한 LSI회로는 1974년쯤에 컴퓨터의 메인메모리와 2세대 마이크로프로세서에 쓰이기 위해 생산되기 시작했다.

VLSI

편집발전과정의 마지막단계는 1980년대 시작해서 지금까지 이어지고 있는 것으로, VLSI(Very Large Scale Integration)이다. VLSI는 10,000~1,000,000개의 트랜지스터를 포함하는 대규모 칩이다, 대형 마이크로프로세서, 단일 칩 마이크로프로세서(single-chip microprocessor) 등을 포함한다. 이 발전은 1980년대 초기 수십만 개의 트랜지스터로 시작해서 2009년 수십억 개의 트랜지스터를 넘어서 발전하고 있다.

이 정도로 조밀성을 높이기 위해서는 여러 단계의 발전이 필요하다. 생산 기업들은 수율을 유지하면서 더 많은 트랜지스터를 포함하는 칩을 만들 수 있도록 세밀한 설계와 깨끗한 생산시설을 추구했다. 공정 향상은 ITRS(International Technology Roadmap for Semiconductor, 국제 반도체 기술 로드맵)로 요약할 수 있다. 설계 툴은 이런 설계를 합리적인 시간에 끝낼 수 있도록 발전했다. CMOS는 에너지 면에서 더 효율적이기 때문에, 전력소비의 증가를 피하면서 NMOS(N-channel metal oxide semiconductor, N형 금속 산화막 반도체)와 PMOS(P-channel metal oxide semiconductor,P형 금속 산화막 반도체)를 대체했다. 1986년에 백만 개가 넘는 트랜지스터를 포함하는 최초의 1Mb 크기의 랩이 소개되었다. 1989년 마이크로프로세서 칩에는 백만 개가 넘는 트랜지스터가 들어갔고, 2005년에는 십억 개의 트랜지스터가 들어갔다[17]. 기술의 발전은 조금도 수그러들지 않고, 2007년에는 수백억 개의 메모리 트랜지스터가 들어간 칩이 개발되었다.[18]

ULSI, WSI, SOC, 3D-IC

편집복잡성이 더욱 커진 것을 반영하는 ULSI(Ultra-Large-Scale Integration)는 백만 개가 넘는 트랜지스터를 포함하는 초대규모 집적을 의미한다[19]. 트랜지스터를 1,000,000개 이상 포함하고, 인텔의 486이나 펜티엄이 ULSI에 해당한다. VLSI와 ULSI를 정확하게 구분하기는 어렵다.

웨이퍼 규모 집적은 한 개의 "슈퍼칩"을 만들기 위해 전체 실리콘 웨이퍼를 사용하는 매우 큰 집적회로를 만드는 것을 의미한다. WSI(Wafer-Scale Integration)는 큰 규모와 줄어든 패키징을 통해 특히 병렬 슈퍼컴퓨터 같은 일부 시스템에서 매우 급격히 비용을 줄였다. WSI라는 이름은 WSI가 개발되었을 때의 기술의 발전 단계인 VLSI에서 유래되었다[20]. SOC(System-On-a-Chip)는 컴퓨터나 다른 시스템에 필요한 모든 소자들이 한 개의 칩에 포함된 집적 회로이다. 이런 기기의 설계는 매우 복잡하고 비용이 들며, 한 조각의 실리콘에 모든 이질적인 소자들을 포함시키는 것은 특정 소자의 효율성을 희생시킬 수도 있다. 하지만 이런 결점들은 적은 제조 비용과 조립 비용, 상당히 줄어든 전력 소모로 상쇄될 수 있다. 소자들 간의 모든 신호가 한 개의 실리콘에서 교환되기 때문에 훨씬 적은 전력이 필요하다[21].

3차원 집적 회로는 한 개의 회로에 수직과 수평으로 집적된 2개 이상의 활성 전자 소자의 층이 있다. 층간의 통신은 한 개의 실리콘에서 일어나는 신호를 이용하며 결과적으로 전력 소모가 분리된 동일한 회로보다 더 적게 든다. 짧은 수직 회로 선을 이용하는 것은 더 빠른 작동을 위해 전체 회로 선의 길이를 상당히 줄일 수 있다[22].

집적 회로에서의 발전

편집코어나 마이크로프로세서는 컴퓨터나 휴대폰부터 전자레인지까지 모든 것을 통제하는 가장 발전한 집적 회로이다. 디지털 메모리칩과 ASIC는 현대 정보사회에서 중요한 집적 회로의 다른 예이다. 복잡한 집적 회로를 설계하고 개발하는 비용은 꽤 높지만 각각의 집적 회로의 비용은 보통 수백만 개의 제품에 사용되면서 낮아진다. 집적 회로는 작은 크기로 인해 빠른 작동이 가능하게 하는 저 전력 논리회로를 구현 가능하게 하기 때문에 성능이 좋다.

집적 회로는 한 칩에 더 많은 회로가 내장될 수 있도록 작은 크기를 지향해 왔다. 이것은 비용을 줄이거나 더 많은 기능을 할 수 있도록 집적회로의 용량을 늘려왔다. 무어의 법칙에서는 2년마다 집적 회로에 포함되는 트랜지스터의 개수가 2배씩 늘어난다고 한다. 일반적으로 크기가 줄어들수록 거의 모든 것이 향상된다. 비용과 전력 소모는 줄고 속도는 올라간다. 하지만 나노미터 크기의 집적 회로는 누설전류 같은 문제가 발생한다. 이 문제는 현재 하이-k 유전체로 해결하고 있다. 이런 속도저하와 전력소모가 최종사용자에게는 분명히 느껴지기 때문에 더 정밀한 집적 회로를 생산하기 위한 제조 기업들간의 치열한 경쟁이 있다. 이런 과정과 몇 년 안에 일어날 것으로 예상되는 발전은 ITRS가 묘사하고 있다.

현재의 연구 프로젝트에서 집적 회로는 생체전자공학이나 의학 삽입물에서 센서로 사용될 목적으로 개발되고 있다. 각각의 봉합은 노출된 반도체 물질에 의한 부식이나 분해를 막기 위해 유기물로 이뤄져야 한다[23]. CMOS에서 사용되는 이런 소수의 물질들 중 하나로, 의료삽입물에서 전극역할에 접합하고 안정하다고 밝혀진 질화티타늄(TiN)이 있다[24][25].

분류

편집집적 회로는 아날로그, 디지털, 그리고 아날로그와 디지털을 혼합한 것으로 분류할 수 있다.

디지털 집적 회로는 몇 제곱밀리미터 안에 한 개부터 수백만 개의 논리게이트, 플립-플랍, 멀티플렉서 등을 포합할 수 있다. 집적 회로는 작은 크기에 비해 빠른 속도, 작은 손실 전력, 제조 비용의 절감을 가능하게 한다. 이 디지털 집적 회로는 0과 1의 신호를 처리하며 마이크로프로세서, DSP, 마이크로컨트롤러 등에서 쓰인다.

센서나 전력관리 회로, 연산증폭기 같은 아날로그 집적 회로는 연속적인 처리 신호로 작동한다. 이것들은 증폭이나 능동필터링, 복조, 믹싱 같은 기능을 한다. 아날로그 집적 회로는 전문가들이 설계한 아날로그 회로를 제공하기 때문에 회로 설계하는 사람들이 어려운 아날로그 회로를 설계를 처음부터 해야하는 부담을 줄여준다.

집적회로는 또한 A/D변환기나 D/A변환기 같은 기능을 하기 위해 한 칩에 아날로그와 디지털 회로가 동시에 포함되어 있는 것도 있다. 이런 혼합신호 회로는 더 작은 크기와 더 낮은 비용이 들지만, 신호 간섭에 주의해야 한다.

현대의 전자 소자 배전기는 매우 다양한 집적 회로의 하위 항목이 있다.

- 디지털 집적 회로는 논리회로, 메모리 칩, 인터페이스 집적 회로(레벨 시프터, 직렬자/역직렬자 등), 전력 관리 IC, 그리고 프로그램 가능한 기기같은 하위 항목이 있다.

- 아날로그 집적 회로는 리니어 IC나 RF IC로 나뉜다.

- 혼합 신호 집적 회로는 A/D. D/A 변환기 같은 데이터 수집 집적 회로, 디지털 포텐셔미터, 클록/타이밍 집적 회로로 나뉘어 진다.

제조

편집공정

편집주기율표상의 반도체 물질의 화합물은 고체 진공관에 가장 적합한 물질로 여겨졌다. 산화구리부터 시작해서 게르마늄 그리고 실리콘 같은 물체들은 조직적으로 1940년대와 1950년대에 연구되었다. 오늘날, 일부 III-V화합물이 LED나 레이저, 태양전지, 빠른 속도의 회로 등 특정한 곳에 사용되기는 하지만, 집적회로의 기판은 주로 단결정 실리콘이다. 반도체 물질의 결정구조에 결함이 생기지 않게 하면서 결정을 만드는 방법을 개발하는데 수십 년이 걸렸다.

반도체 칩은 이미징, 증착, 식각공정이라는 세 가지 주요한 단계를 거쳐 제조된다. 이런 세 가지 과정 외에 부가적으로 도핑과 연마라는 과정이 있다.

단결정 실리콘 웨이퍼(목적에 따라, 실리콘에 세피아나 비화 갈륨 웨이퍼를 사용한다)는 기판으로 사용된다. 사진석판술은 도핑되거나 절연체, 알루미늄같은 금속 소자들이 배치되어야 할 기판의 위치를 표시하는데 사용된다.

- 집적회로는 많은 겹겹이 쌓여진 층으로 구성되어 있고, 각각은 사진석판술로 디파인되었으며, 보통 다른 색을 가진다. 확산층에선 다양한 도판들이 기판으로 확산되고, 주입층은 추가적인 이온을 주입하고, 폴리실리콘이나 금속 층은 도체를 디파인하고, 접촉층을 통해서 도체 층 사이에 연결을 디파인 한다. 모든 소자들은 이런 층들의 특정한 조합으로 구성된다.

- 셀프 얼라인 CMOS 공정에서, 트랜지스터는 게이트 층이 확산층을 가로지르는 모든 곳에서 생성된다.

- 축전구조는 전통적인 전기적 축전기의 평행도체판과 모양이 매우 닮았고, 플레이트 사이에 절연체가 있음으로서 생성된다. 집적회로에 사용되는 축전기의 크기는 다양하다.

- 다양한 길이의 곡류무늬는 대부분의 논리회로가 저항기를 필요로 하지는 않지만, 보통 온칩 저항기를 만드는데 이용된다. 그것의 면적저항률과 결합하여, 면적에 따른 길이의 비율이 저항성을 결정한다.

- 드물게, 작은 온칩코일이나 자이레이터로 절연구조가 생성될 수 있다.

CMOS장치가 논리상태간의 전이에서만 전류를 쓰기 때문에, CMOS장치는 접합형 트랜지스터보다 전류를 덜 소모한다.

RAM은 집적 회로의 가장 전형적인 종류이다. 고로, 고밀도의 장치들은 메모리라고 할 수 있다. 하지만 심지어 마이크로프로세서도 칩에 메모리를 포함할 수 있다, 첫 번째 사진밑의 어레이 배열 구조를 참고하라. 구조는 복잡하지만 층은 넓이보다 훨씬 얇다. 제조과정은 사진석판술과 비슷하지만 가시광선 영역의 빛은 층을 노광할 수 없다. 가시광선 대신 자외선 같은 더 높은 주파수 영역의 광자들이 각각의 층에 패턴을 만드는데 사용된다. 각각의 패턴들이 너무 작기 때문에 제조공정을 수정하려면 전자 현미경이 필수적이다.

각각의 장치는 ATE(Automated Test Equipment)를 사용해서 패키징 전에 테스트를 받는다. 그러고 나서 웨이퍼는 다이라고 불리는 직사각형의 블록으로 자른다. 각각의 다이는 그러고 나서 주로 다이의 겉부분에서 발견되는 패드에 열음파 결합을 한 알루미늄이나 금 본딩와이어에 연결된다[26]. 열음파 결합은 처음 이런 필수적인 전자 소자들을 외부와 연결하는 믿을 만한 방법으로 A.Coucoulas에 의해 소개되었다. 패키징 한 후에, 장치들은 웨이퍼 프로브에서 사용된 ATE와 같거나 비슷한 것들을 이용해서 마지막 검사를 한다. 산업용 CT도 사용될 수 있다. 검사는 저비용 제품에서는 제조비용의 25프로를 넘게 차지하지만, 소량생산, 고비용 제품에서는 무시할 만한 수준이다.

2005년을 기준으로 반도체 제조 시설은 짓는데 10억 달러 이상이 들어간다[27]. 제조 시설을 짓는데 드는 비용은 많은 공정이 자동화되어 있다는 점에서 록의 법칙에 따라 시간이 흐를 수록 올라간다. 오늘날 가장 발전된 공정들은 다음과 같은 기술을 사용한다.

- 직경 300mm의 웨이퍼

- 32나노미터 이하의 제조공정. 인텔, IBM, NEC, AMD는 CPU칩에 32나노 미터 이하의 제조공정을 한다. IBM과 AMD는 45nm공정에 액침노광을 사용한다.

- 상호연결을 위해 구리가 알루미늄을 대체하는 구리배선

- 저유전 절연체

- 실리콘 절연체

- SSDOI(strained silicon directly on insulator)로 알려진 IBM의 변형실리콘

- 인텔이 2011년부터 22nm공정에 사용하고 있는 트라이게이트 트랜지스터 같은 멀티게이트

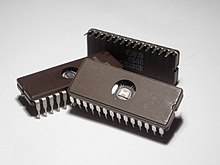

패키징

편집집적 회로는 다른 기능소자와 결합하여 전체 회로가 구성된다. 따라서 패키지를 통해 PCB상에 결합하여 회로를 구성한다. 개별적인 칩이 하나의 패키지 형태를 갖는 것이 기본이다. 패키지를 만들어 PCB상에 붙이는 방법이 일반적이지만, 비용 상 또는 다른이유로 PCB상에 직접 붙이는 방법도 사용한다.

본딩을 할 때 반도체 칩을 PCB 상에 고정하고 반도체칩과 PCB상의 패드에 직접 연결한다. 와이어본딩이 보이면 손상을 받을 수 있으므로 보호용 재료로 덮는다.

이렇게 직접 PCB에 칩을 붙이는 방법은 문자 LCD와 같은 기능적 블럭이나 장난감 등에 비용에 민감한 분야에 적용하여 전자회로를 구현한다.

PCB상에 직접 칩을 붙이면 칩만 제거하는 일이 불가능하므로 고장시 모듈 전체를 바꾸는 방법으로 시스템 관리 유지한다. 모듈로 기능적 블럭이 확실한 경우에 많이 사용한다.

초기 집적 회로는 세라믹 평판에 패키지되었고, 그 방법은 몇 년간 군이 안정성과 작은 크기를 위해 채용하였다. 상업용 회로 패키징은 빠르게 DIP(dual in-line package)로 이동했고, 처음에는 세라믹을 이용했으나 나중엔 플라스틱을 이용했다. 1980년대 VLSI회로의 핀 카운트는 DIP패키징의 한계를 넘어섰고, PGA(Pin Grid Array)나 LCC(Leadless Chip Carrier)패키지로 이동했다. 표면 실장 기술은 1980년대에 나타나기 시작해 1980년대 후반에 널리 퍼졌다.

1990년대 후반, PGA패키지가 고성능 마이크로프로세서에 종종 쓰이긴 했지만, PQFP와 TSOP패키지가 하이 핀 카운트 장치에 흔하게 쓰였다. 인텔과 AMD는 현재 PGA패키지에서 LGA(Land Grid Package)로 바꾸는 추세이다.

BGA(Ball Grid ARRAY)패키지는 1970년대부터 존재했다. FBGA(Flip-chip Ball Grid Array)패키지는 다른 패키지 방식보다 훨씬 더 높은 핀 카운트를 지원하는데 1930년대에 개발되었다. FCBGA패키지에서 다이가 거꾸로 마운트되고, 선보다는 인쇄 회로 기판비슷한 패키지 기판을 통해서 패키지 볼에 연결된다. FCBGA패키지는 입력/출력 신호의 배열이 다이 주변에 한정되기 보다는 전체 다이에 분배될 수 있게 해준다.

여러개의 다이가 한 패키지에 포함되면 그것은 SiP(System in Package)라고 한다. 여러개의 다이가 보통 세라믹인 한 개의 작은 기판에 결합되면 MCM(Multiple-Chip Module)이라고 한다. 큰 MCM과 작은 인쇄 회로 기판 사이의 구별은 종종 혼란스럽다. 패키지 형태에 따라 DIP(Dual Inline Package), TO, SIP(Single Inline Package), 평면 패키지로 나뉠 수 있다.

칩 라벨링과 제조일자

편집대부분의 집적 회로는 제조기업의 이름이나 로고, 부품 생산 배치 넘버, 시리얼 넘버 그리고 언제 제조되었는지를 표기하는 4자리의 숫자, 이 4개의 정보를 포함할 수 있을 정도로 크다. 극히 미세한 표면 실장 기술은 칩의 특성을 표시하는 제조 기업의 순람표에 쓰이는 한 개의 숫자만을 표기한다.

제조 일자는 보통 연도를 표시하는 2자리 숫자와 주를 표시하는 2자리 숫자로 이루어져있다. 예를 들어 8341은 1983년 41번 째 주에 생산되었다는 말이다.

제조회사 표기

편집- KA : 삼성

- CD : RCA

- HA : 히타치

- LM : 내셔널

- MC : 모토로라/프리스케일 세미컨덕터

- NE : 시그네틱스

- SN : 텍사스 인스트루먼트

- TC : 도시바

- XR : EXAR

지적재산권

편집집적회로 설계를 보호하는 법안들은 집적회로의 각각의 층이나 광학 마스크를 베낄 가능성에서 비롯된 것이다.

1989년 워싱턴에서 IPIC조약을 채택한 외교회의가 열렸다. IPIC조약은 지금은 효력의 없지만 TRIPS합의에서 부분적으로 통합되었다.

집적회로 설계디자인을 보호하는 법이 많은 나라에서 채택되고 있다.

다른 발전

편집1980년대 설계가능논리소자가 개발되었다. 이 장치들은 논리 함수와 연결성을 사용자가 설계할 수 있는 회로를 포함한다. 이것은 한 개의 칩이 논리 함수, 가산기, 레지스터 같은 다른 LSI 함수를 실행할 수 있도록 설계하게 한다. 현재 FPGA(Field Programmable Gate Array)라고 불리는 장치들은 동시에 수 만개의 LSI 회로를 실행시킬 수 있고, 1.5GHz까지 작동한다.

지난 30년간 집적회로 산업에 최적화된 기술들은 미세전자기계시스템으로 알려진 기술을 이용하는 매우 작은 기계 장치를 만드는데 사용되어 왔다. 이런 장치들은 다양한 상업적, 군사적 목적들을 수행한다. 예를 들어 DLP프로젝터, 잉크젯 프린터, 가속계와 자동차 에어백에 사용되는 MEMS자이로스코프 같은 것 들이 있다.

2014년, 평면에 2차원 플레이너 공정을 하는 방식으로 한 개 층이나 실리콘 칩의 한 면에 수 많은 트랜지스터들이 생산되고 있다. 연구원들은 다음과 같은 여러 유망한 대안들의 프로토타입을 생산했다.

- 작은 실리콘 구의 전체 표면에 트랜지스터를 생산하는 것[29][30]

- 3차원 집적회로나 모놀리식 3D, 적층 본딩와이어 같은 여러겹의 쌓여진 트랜지스터의 접근 방법[31] stacked wire bonding,[32].

- 다른 물질로 만들어진 트랜지스터:그래핀 트랜지스터, 탄소 나노튜브 전계 효과 트랜지스터, 질화 갈륨 트랜지스터, 트랜지스터와 유사한 나노와이어 전자기기, 유기전계효과 트랜지스터 등.

- 말 수 있는 컴퓨터를 실현 가능케 할 기판에서의 변화. 예를 들어, 플렉서블 트랜지스터, 플렉서블 디스플레이나 다른 플렉서블을 응용한 전자기기.

과거에는, 라디오는 마이크로프로세서같은 저비용 공정으로는 생산될 수 없었다.하지만 1998년부터, 많은 수의 라디오 칩들이 CMOS공정을 이용하여 개발되었다. 예를 들어 인텔의 DECT 무선 전화기나 Atheros의 802.11카드가 있다.

이미 인텔과 AMD이 사용중인 멀티코어나 멀티 프로세서패러다임의 뒤를 잇는 발전이 일어날 것으로 보인다. Rapport Inc나 IBM은 2006년 256코어 마이크로프로세서인 KC256을 생산하기 시작했다. 인텔은 2011년 2월에서 8월까지, 판매용은 아니지만, 80코어의 프로토타입을 공개했다. 각각의 코어는 다른 것들과는 독립적으로 작업을 처리할 수 있다. 이 디자인은 칩프로그래밍에 새로운 도전을 부여한다. 오픈소스인 X10같은 병렬 프로그램 언어가 이작업을 돕기위해 설계되었다[33].

2000년대 초반부터, 모듈레이터, 감지기, 라우팅 같은 CMOS에 기초한 광학 기기를 결합한 집적 광 송수신기에 기초한 실리콘의 성공적인 상용화의 결과로 학문적 연구나 산업 분야에서 광학 기능의 통합이 활발하게 연구되고 있다[34].

각주

편집- ↑ “아리조나에 새 공장을 짓는데 50억달러가 넘는 돈을 투자하는 인텔”. 2013년 2월 3일에 확인함.

- ↑ “인텔® 22nm 기술”. 2014년 7월 26일에 확인함.

- ↑ “Integrated circuit (IC)”. JEDEC.

- ↑ Andrew Wylie (2009). “The first monolithic integrated circuits”. 2014년 7월 7일에 원본 문서에서 보존된 문서. 2011년 3월 14일에 확인함.

하지만, 일반적인 집적회로의 용법은 모놀리식 집적 회로라고 알려진 한 조각의 회로를 말한다.

- ↑ Horowitz, Paul; Hill, Winfield (1989). 《The Art of Electronics》 2판. Cambridge University Press. 61쪽. ISBN 0-521-37095-7.

집적 회로는 이산 트랜지스터로 만든 많은 회로를 대체시켰는데, 반도체 물질의 한 칩으로부터 만든 단지 트랜지스터와 다른 소자의 배열일 뿐이다.

- ↑ “Integrated circuits help Invention”. Integratedcircuithelp.com. 2012년 10월 11일에 원본 문서에서 보존된 문서. 2012년 8월 13일에 확인함.

- ↑ W. Jacobi/SIEMENS AG: "Halbleiterverstärker" priority filing on 14 April 1949, published on 15 May 1952.

- ↑ "The Hapless Tale of Geoffrey Dummer" Archived 2013년 5월 11일 - 웨이백 머신, (n.d.), (HTML), Electronic Product News, accessed 8 July 2008.

- ↑ George Rostky, (n. d.), "Micromodules: the ultimate package", (HTML), EE Times, accessed 8 July 2008.

- ↑ The Chip that Jack Built, (c. 2008), (HTML), Texas Instruments, Retrieved 29 May 2008.

- ↑ Winston, Brian (1998). 《Media Technology and Society: A History : From the Telegraph to the Internet》. Routledge. 221쪽. ISBN 978-0-415-14230-4.

- ↑ “Texas Instruments – 1961 First IC-based computer”. Ti.com. 2012년 8월 13일에 확인함.

- ↑ Nobel Web AB, (10 October 2000),(The Nobel Prize in Physics 2000, Retrieved 29 May 2008

- ↑ Kurt Lehovec's patent on the isolation p–n junction: 미국 특허 3,029,366 granted on 10 April 1962, filed 22 April 1959. Robert Noyce credits Lehovec in his article – "Microelectronics", Scientific American, September 1977, Volume 23, Number 3, pp. 63–9.

- ↑ Peter Clarke, Intel enters billion-transistor processor era, EE Times, 14 October 2005 Archived 2013년 5월 10일 - 웨이백 머신

- ↑ 임석구, 홍경호 디지털 논리회로: 이론 실습 시뮬레이션, 37page, HANBIT media, Inc. Printed in korea, 2009 초판, ISBN 978-89-7914-600-4

- ↑ Peter Clarke, EE Times: Intel enters billion-transistor processor era, 14 November 2005

- ↑ Antone Gonsalves, EE Times, "Samsung begins production of 16-Gb flash", 30 April 2007

- ↑ Meindl, J.D. “Ultra-large scale integration”. 《ieee.org》. IEEE. 2014년 9월 21일에 확인함.

- ↑ Shanefield, Daniel. “Wafer scale integration”. 《google.com/patents》. 2014년 9월 21일에 확인함.

- ↑ Klaas, Jeff. “System-on-a-chip”. 《google.com/patents》. 2014년 9월 21일에 확인함.

- ↑ Topol, A.W.; Tulipe, D.C.La; Shi, L; et., al. “Three-dimensional integrated circuits”. 《ieee.org》. International Business Machines Corporation (IBM). 2014년 9월 21일에 확인함.

- ↑ A.H.D. Graham, J. Robbins, C.R. Bowen, J. Taylor (2011). “Commercialisation of CMOS Integrated Circuit Technology in Multi-Electrode Arrays for Neuroscience and Cell-Based Biosensors”. 《Sensors》 11: 4943–4971. doi:10.3390/s110504943.

- ↑ H. Hämmerle, K. Kobuch, K. Kohler, W. Nisch, H. Sachs, M. Stelzle (2002). “Biostability of micro-photodiode arrays for subretinal implantation”. 《Biomat.》 23: 797–804. doi:10.1016/S0142-9612(01)00185-5.

- ↑ M. Birkholz, K.-E. Ehwald, D. Wolansky, I. Costina, C. Baristyran-Kaynak, M. Fröhlich, H. Beyer, A. Kapp, F. Lisdat (2010). “Corrosion-resistant metal layers from a CMOS process for bioelectronic applications” (PDF). 《Surf. Coat. Technol.》 204 (12–13): 2055–2059. doi:10.1016/j.surfcoat.2009.09.075.

- ↑ Coucoulas, A., http://commons.wikimedia.org/wiki/File:Hot_Work_Ultrasonic_(Thermosonic)_Bonding_549-556.pdf Archived 2014년 12월 20일 - 웨이백 머신 “Hot Work Ultrasonic Bonding – A Method Of Facilitating Metal Flow By Restoration Processes”, Proc. 20th IEEE Electronic Components Conf. Washington, D.C., May 1970, pp. 549–556.https://sites.google.com/site/hotworkultrasonicbonding/

- ↑ For example, Intel Fab 28 cost $3.5 billion, while its neighboring Fab 18 cost $1.5 billion http://www.theinquirer.net/default.aspx?article=29958 Archived 2007년 1월 3일 - 웨이백 머신

- ↑ “145 series ICs (in Russian)”. 2012년 4월 22일에 확인함.

- ↑ "Spherical semiconductor radio temperature sensor" Archived 2009년 1월 7일 - 웨이백 머신. NatureInterface. 2002.

- ↑ NOBUO TAKEDA. "MEMS applications of Ball Semiconductor Technology" Archived 2015년 1월 1일 - 웨이백 머신.

- ↑ Zvi Or-Bach. "Why SOI is the Future Technology of Semiconductors" Archived 2014년 11월 29일 - 웨이백 머신. 2013.

- ↑ "Samsung’s Eight-Stack Flash Shows up in Apple’s iPhone 4" Archived 2014년 11월 29일 - 웨이백 머신. 2010.

- ↑ Biever, C. "Chip revolution poses problems for programmers", New Scientist (Vol 193, Number 2594)

- ↑ A. Narasimha; 외. (2008). “A 40-Gb/s QSFP optoelectronic transceiver in a 0.13 µm CMOS silicon-on-insulator technology”. 《Proceedings of the Optical Fiber Communication Conference (OFC)》: OMK7.