표면 실장 기술

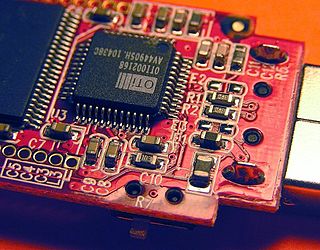

표면 실장 기술 (表面實裝技術, surface mount technology, SMT)은 인쇄 회로 기판 (PCB)의 표면에 직접 실장할 수 있는 표면 실장 부품 (surface mounted components, SMC)을 전자 회로에 부착시키는 방법이다. 이렇게 만들어진 전자 소자는 표면 실장 소자(surface-mount devices, SMD)라고 한다. 전자 산업에서, 표면 실장 기술은 소자핀을 인쇄 회로 기판의 구멍에 끼우는 부품을 사용한 스루홀 기술 부착 방식을 대체했다.

일반적으로 표면 실장 부품은 동일한 스루홀 부품보다 작다. 왜냐하면 표면 실장 부품의 핀은 더 짧거나 전혀 없을 수 있기 때문이다. 표면 실장 부품은 핀이 더 짧으면서, 평면 접촉, 볼 배열 (BGA), 부품의 패키지 위로 나온 핀같이 다양한 종류의 패키지가 있다.

역사

편집표면 실장 기술은 1960년대에 개발되었고 1980년대 후반부터 널리 사용되었다. 표면 실장 기술에서 가장 큰 업적을 남긴 기업은 IBM이다. 부품은 인쇄 회로 기판의 표면에 직접 납땜할 수 있도록 작은 금속핀을 지니도록 기계적으로 다시 설계되었다. 부품은 무척 작아졌고 기판 양면의 부품 배치는 스루홀 실장보다 더 많은 부품을 실장할 수 있게 되어서, 높은 수준의 회로설계를 가능하게 했다. 경우에 따라서 땜납만으로 부품을 기판에 고정하고, 기판의 아래면이나 "두 번째" 면에 있는 부품은 잘 접착된 한곳을 임시적으로 고정시킨다. 일반적으로 표면 실장 소자는 물리적으로 작게 제조하기 때문에 가볍다. 자동화된 고온 표면 실장 부착은 노동비용을 감소시키고 양품의 비율이 크게 증가한다. 표면 실장 소자는 동일한 스루홀 부품을 사용한 기판의 크기와 무게를 1/4에서 1/10까지 줄일 수 있고 비용은 1/2에서 1/4까지 감소시킬 수 있다.

조립 기술

편집부품은 평평한 인쇄 회로 기판에 배치된다. 일반적으로 부품의 주석핀은 납땜 패드라고 불리며 구멍이 없고 은이나 금도금된 구리 패드에 위치한다. 끈적거리는 융제와 땜납 가루를 섞은, 땜납풀은 최초에 스테인레스강 틀판을 사용하여 기판의 모든 납땜 패드에 공급된다. 만약 부품이 반대면에 부착되어 있으면, 수치 제어 장비는 적은 양의 접착 용액점을 반대면 부품의 모든 위치에 칠한다. 그러면 집어서 배치하는 장비는 컨베이어 벨트에서 제공되는 부품을 기판에 배치하는 작업을 한다. 일반적으로 작은 표면 실장 소자는 종이테입이나 플라스틱테입에 부착된 상태로 릴에 감겨서 제공된다. 수치 제어로 집어서 배치하는 장비는 릴이나 튜브에서 부품을 떼어서 인쇄 회로 기판에 배치시킨다. 두 번째면 부품은 최초에 배치하고, 접착점은 낮은 가열기나 자외선 방사 기구로 빠르게 처리한다. 기판은 빠르게 움직이고 첫 번째면 부품은 추가적인 수치 제어 장비가 배치한다.

기판은 리플로우 납땜 오븐으로 운반된다. 처음에는 살짝 가열하는 구역에 들어가고, 기판과 모든 부품의 온도는 점차 균일하게 상승한다. 리플로우 납땜 오븐은 납땜한 이후에 조립된 기판을 냉각시킬때 온도 스트레스를 최소로 줄여주는 역할을 한다. 기판이 들어간 구역의 온도는 땜납풀에 있는 땜납 가루가 녹을 수 있도록 충분히 상승하여, 부품핀을 인쇄 회로 기판의 패드에 결합시킨다. 녹은 땜납의 표면 장력은 적절한 곳에 부품이 위치하도록 한다. 즉, 땜납 패드 평면이 정확하게 설계되었다면 표면 장력은 부품을 정확한 패드에 자동으로 정렬시킨다. 리플로우 납땜은 다양한 기술이 있다. 그중에 적외선 램프를 사용하는 방법이 있다; 적외선 랩프를 사용한 리플로우 땜납 기술은 적외선 리플로우라고 불린다. 또다른 방법으로 뜨거운 가스를 사용하는 방법이 있다. 한번에 특별한 플루오르화탄소 액체를 기상 리플로우 방법을 사용하여 높은 끓는점까지 가열시킨다. 환경적인 문제로 인하여, 기상 리플로우 방법은 인기가 떨어지고 있다. 오늘날, 리플로우 납땜은 대류 오븐에 질소 가스나 농축된 질소 가스를 사용한 방법이 더 일반적으로 사용된다. 각각의 방법은 장점과 단점이 있다. 적외선 리플로우 방법을 사용할 경우에, 기판 설계자는 반드시 작은 부품이 큰 부품의 그림자에 가려지지 않도록 기판을 설계해야 한다. 만약 설계자가 기상 리플로우나 대류 납땜 방법을 알고 있어서 이런 방법으로 제품을 생산하면, 부품 배치는 덜 제한된다. 명확히 불규칙적이거나 열에 민감한 부품의 리플로우 납땜은 수작업으로 부착하여 납땜되거나, 초점을 맞추는 적외선 빔 (focused infrared beam) 장비를 사용하여 큰 기판을 자동으로 납땜할 수 있다.

납땜이 끝난후에, 기판은 근접한 부품 핀끼리 단락을 발생시킬 수 있는 융제와 땜납 가루 잔여물을 제거하도록 세척한다. 송진 융제는 플루오르화탄소 솔벤트, 높은 인화점 탄화수소나 오렌지 껍질에서 유래된 리모넨으로 제거할 수 있다. 수성 융제는 중성수와 세제를 공기 분사하여 잔여물을 빠르게 제거할 수 있다. 미학이 중요하지 않고 융제가 인쇄 회로 기판을 단락시키거나 부식시키지 않을 경우에, 융제 잔여물은 세척되지 않은 채로 기판에 남겨질 경우도 있다. 왜냐하면 기판 세척과 폐기물 제거의 비용을 줄일 수 있기 때문이다.

마지막으로, 기판은 광학적으로 빠지거나 잘못 배치된 부품이 없는지 납땜이 잘 됐는지를 검사한다. 필요할 경우에, 잘못된 인쇄 회로 기판은 재납땜 사업장으로 보내지고 수작업 기술자는 문제점을 찾아서 고친다. 고친 기판은 다시 검사 사업장으로 보내져서 잘 작동하는지 검사한다.

주요 장점

편집오래된 스루홀 기술과 비교해서 표면 실장 기술의 주요 장점은 다음과 같다:

- 부품이 작고 가볍다.

- 더 적은 구멍으로 보드를 가공할 수 있다.

- 간단하게 자동으로 조립할 수 있다.

- 부품은 정확하게 자동으로 배치해서 오류가 적게 발생된다. (녹은 땜납의 표면 장력은 부품핀을 땝납 패드로 당겨서 정확한 위치에 배열시킨다.)

- 부품은 인쇄 회로 기판의 양면에 부착시킬 수 있다.

- 부품핀의 저항과 임피던스가 감소된다. (부품의 성능과 동작 주파수가 증가된다.)

- 흔들리거나 진동 상태에서 기계적인 성능이 우수하다.

- 일반적으로 표면 실장 부품은 스루홀 부품보다 가격이 싸다.

- 표면 실장 기술은 스루홀 기술보다 불필요한 RF 신호 효과가 적게 발생하고, 부품 특성의 유연성이 크게 향상된다.

주요 단점

편집- 표면 실장 기술의 제조 공정은 스루홀 기판보다 정교한 기술이 필요하기 때문에, 제품을 생산하기 위한 초기 비용이 비싸고 초기 설정 시간도 오래 걸린다.

- 표면 실장 소자의 크기와 핀간격이 매우 작아서 수작업 하기가 매우 힘들기 때문에, 소자 수준의 부품 수리가 어렵다.

불량 표면 실장 부품 재부착

편집불량 표면 실장 부품은 재작업 시스템을 사용하여 고칠 수 있다. 일반적으로 재작업 과정은 기술자나 재작업 장비가 아래와 같은 단계를 통하여 오류의 종류를 찾아서 고친다:

- 땜납을 녹여서 부품을 제거한다.

- 잔류 땜납을 제거한다.

- 직접 부품이 인쇄된, 인쇄 회로 기판에 땜납풀을 인쇄한다.

- 새로운 부품을 배치하여 재부착한다.

인쇄 회로 기판을 고치기 위해서 동일한 부품의 수백개에서 수천개가 필요한 경우도 있다. 조립으로 인한 오류는 공정 중에 발견할 수 있다. 그러나 부품불량으로 발생되는 완전히 새로운 단계의 재작업은 발견하는 데 너무 오래 걸리고, 경우에 따라서 실사용자가 오류를 경험하기 전까지 제조사가 발견하지 못하기도 한다. 재작업은 고가치 제품을 만드는 데 필요한 리비전이나 부품기반의 펌웨어를 변경하여 낡은 제품을 새롭게하는 리엔지니어링에도 사용될 수 있다. 이런 작업은 제품의 부품을 수리/교체하도록 특별하게 설계된 곳의 재작업 과정이 필요하다.

공융점 땜납은 소형 재작업에 사용되기도 한다.

패키지 크기

편집일반적으로 표면 실장 부품은 핀번호를 세는 방법이 비슷하고 사람보다 기계가 취급하기 쉽게 설계되어 있다. 전자 산업은 패키지 모양과 크기가 표준화되어 있다. (표준화를 선도하는 단체로 JEDEC가 있다.) 패키지의 종류는 다음과 같다:

- 2단자 패키지

- 직사각형 수동 소자 (일반적으로 저항기와 축전기):

- 01005: 0.016" x 0.008" (0.4 mm x 0.2 mm)

- 0201: 0.024" x 0.012" (0.6 mm x 0.3 mm)

- 0402 (1005): 0.04" x 0.02" (1.0 mm x 0.5 mm)

- 0603 (1608): 0.063" x 0.031" (1.6 mm x 0.8 mm)

- 0805 (2012): 0.08" x 0.05" (2.0 mm x 1.25 mm)

- 1206 (3216): 0.126" x 0.063" (3.2 mm x 1.6 mm)

- 1806 (4516): 0.177" x 0.063" (4.5 mm x 1.6 mm)

- 1812 (4532): 0.18" x 0.12" (4.6 mm x 3.0 mm)

- 2512: 0.25" x 0.12" (6.3 mm x 3.0 mm)

- 탄탈 커패시터 [1]:

- A (EIA 3216-18): 3.2 mm x 1.6 mm x 1.6 mm

- B (EIA 3528-21): 3.5 mm x 2.8 mm x 1.9 mm

- C (EIA 6032-28): 6.0 mm x 3.2 mm x 2.2 mm

- D (EIA 7343-31): 7.3 mm x 4.3 mm x 2.4 mm

- E (EIA 7343-43): 7.3 mm x 4.3 mm x 4.1 mm

- SOD: 소형 다이오드(Small Outline Diode):

- SOD-323: 1.7 mm x 1.25 mm x 0.95 mm

- SOD-123: 3.68 mm x 1.17 mm x 1.60 mm

- SOD-80C: 3.50 mm x 1.50 mm x 2.00 mm

- MELF: 금속 전기 표면(Metal ELectrical Face) (일반적으로 저항기와 축전기): 통모양 부품이며, 직경은 동일한 코드의 직사각형 패키지와 같지 않다.

- 0201: L:2.2mm D:1.1mm (납땜패드는 직사각형 0805 패키지와 동일함)

- 0204: L:3.6mm D:1.4mm (납땜패드는 직사각형 1206 패키지와 동일함)

- 0207: L:5.8mm D:2.2mm

- 직사각형 수동 소자 (일반적으로 저항기와 축전기):

- 3단자 패키지

- SOT: 3단자를 지닌 소형 트랜지스터 (small-outline transistor) [2]

- SOT-23: 3 mm x 1.75 mm x 1.3 mm – 단일 트랜지스터는 3단자이며, 집적회로는 8단자로 생산되기도 한다.

- SOT-223: 6.7 mm x 3.7 mm x 1.8 mm – 4단자일 경우에 1단자는 트랜지스터의 발열을 식히는 역할을 한다.

- DPAK (TO-252): 부품 패키지이다. 모토로라가 고출력 소자를 적용하기 위하여 설계했다. 3단자 패키지나 5단자 패키지도 생산된다. [3]

- D2PAK (TO-263) – DPAK 패키지보다 크다; 기본적으로 TO220 스루홀 패키지를 표면 실장 패키지로 개발한 것이다. 3단자, 5단자, 6단자, 7단자, 8단자와 9단자 패키지도 생산된다. [4]

- D3PAK (TO-268) – D2PAK 패키지보다 더 크다. [5]

- SOT: 3단자를 지닌 소형 트랜지스터 (small-outline transistor) [2]

- 4단자초과 패키지 (일반적인 도면은 인터실에서 발견할 수 있다.)

- 딥 (Dual-in-line package, DIP)

- SOIC (소형 집적회로, Small-Outline Integrated Circuit) - 딥, 핀수는 8핀이거나 더 많은 패키지도 있으며, 핀모양은 걸윙식이고 핀간격은 1.27 mm이다.

- TSOP (얇은 소형 패키지, thin small-outline package) - SOIC 패키지보다 얇고 핀간격이 0.5 mm이다.

- SSOP (축소된 소형 패키지, shrink small-outline package) - 핀간격은 0.635 mm이며, 경우에 따라서 0.8 mm인 패키지도 있다.

- TSSOP (얇은 축소된 소형 패키지, thin shrink small-outline package)

- QSOP (1/4크기 소형 패키지, quarter-size small-outline package) - 핀간격은 0.635 mm이다.

- VSOP (매우 소형 패키지, Very Small Outline Package) - QSOP 패키지와 비슷하며; 핀간격은 0.4 mm, 0.5 mm, 0.65 mm가 있다.

- 큅 (Quad-in-line package)

- PLCC (플라스틱 리드 칩 캐리어, Plastic leaded chip carrier) - 정사각형, J형 핀, 핀간격이 1.27 mm이다.

- QFP (4평면 패키지, Quad Flat Package) - 4면으로 핀이 돌출되어 있으며, 패키지의 크기는 다양하다.

- LQFP (낮은 4평면 패키지, Low-profile Quad Flat Package) - 핀간격은 1.4 mm이거나 더 넓고, 4면으로 핀이 돌출되어 있으며, 패키지의 크기와 핀수는 다양하다.

- PQFP (플라스틱 4평면 패키지, plastic quad flat-pack) - 4면으로 핀이 돌출되어 있으며, 핀수는 44이거나 더 많다.

- CQFP (세라믹 4평면 패키지, ceramic quad flat-pack) - PQFP와 비슷하다.

- MQFP (미터식 4평면 패키지, Metric Quad Flat Pack) - QFP 패키지와 비슷하지만 핀간격을 미터방식으로 표기한다.

- TQFP (얇은 4평면 패키지, thin quad flat pack) – PQFP 패키지를 얇게 개선한 패키지이다.

- QFN (노출된 핀이없는 4평면 패키지, Quad Flat package No leads) - QFN 패키지의 패드는 동일한 QFP 패키지의 패드와 비슷하다.

- 리드레스 칩 캐리어 (leadless chip carrier) - 수직으로 깊숙한 곳을 납땜하여 접촉할 수 있다. 일반적으로 기계적인 내구성이 좋기 때문에, 항공전자에 주로 사용된다.

- MLP (마이크로 리드프레임 패키지, Micro Leadframe Package)- 노출된 핀이 없고, 패드간격이 0.5 mm인 리드프레임 패키지이다. [6]

- PQFN (노출된 핀이없는 전력 4평면 패키지, power quad flat-pack no-leads) - 열방출용 다이패드가 노출되어 있다.

- 그리드 배열

- 핀 그리드 배열 (Pin grid array)

- 볼 그리드 배열 (Ball grid array) – 정사각형이나 직사각형의 반도체 패키지 표면에 땜납 볼이 붙어있다. 일반적으로 볼간격은 1.27 mm이다.

- LFBGA (낮고 좋은 간격 볼 그리드 배열, low profile fine pitch ball grid array) – 정사각형이나 직사각형의 반도체 패키지 표면에 땜납 볼이 붙어있다. 일반적으로 볼간격은 0.8 mm이다.

- CGA (Column Grid Array) – 입출력 포인트가 원형 그리드 패턴으로 고온용 땝납이 배열된 패키지이다.

- CCGA (세라믹 원형 그리드 배열, ceramic column grid array) – 입출력 포인트가 원형 그리드 패턴으로 고온용 땜납이 배열된 패키지이다. 부품의 몸체는 세라믹으로 만들어진다.

- μBGA (마이크로 BGA) – 볼 그리드 배열과 비슷하지만 볼간격이 1 mm보다 더 세밀하다.

- LLP (리드레스 패키지, Lead Less Package) – 핀간격 (일반적으로 0.5 mm)을 미터법으로 표기한 패키지이다.

- 비패키지 소자 (표면 실장으로 사용하기 위해서 특별한 조립공정이 필요하다.)

- COB (칩 온 보드, chip-on-board) – 일반적으로 집적회로가 올라간 순수한 실리콘 칩은 비패키지 상태로 제공되고 (일반적으로 리드 프레임은 에폭시로 덮혀져 있음) 직접 인쇄 회로 기판에 부착된다. 칩 온 보드는 와이어 본딩되어 있고 기계적인 충격을 방지하기 위해서 에폭시로 칩을 보호하기도 한다.

- COF (칩 온 플렉스, chip-on-flex) – 칩 온 보드가 개선된 방식중 하나이다. 칩은 플렉서블 전자회로에 직접 부착된다.

- COG (칩 온 유리, chip-on-glass) – 칩 온 보드가 개선된 방식중 하나이다. 칩은 유리의 표면에 직접 부착된다. 일반적으로 액정 디스플레이에서 주로 사용된다.

- 딥 (Dual-in-line package, DIP)

비패키지 소자는 제조사에 따라서 신기한 종류의 다양한 패키지가 있으며 표준화 명칭으로 사용되기도 한다. 인쇄 회로 기판을 설계할때, 설계자는 도면을 확인할 필요가 있다.

같이 보기

편집외부 링크

편집- (영어) 회로 조립 잡지

- (영어) 표면 실장 기술 (포탈사이트)

- (영어) SMT 잡지 Archived 2008년 12월 3일 - 웨이백 머신

- (독일어) 손으로 표면 실장 납땜하기

- (영어) 손으로 표면 실장 기판에 조립하고 납땜하기

- (영어) DIY 표면 실장 오븐 Archived 2006년 2월 18일 - 웨이백 머신

- (영어) 혁신적인 전선 기술