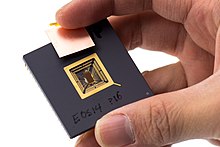

RISC-V

RISC-V("리스크 파이브"로 발음)는 축소 명령어 집합 컴퓨터(RISC) 기반의 개방형 명령어 집합(ISA)이다.

대부분의 ISA와 달리 RISC-V ISA는 어떠한 목적으로는 자유로이 사용할 수 있으며, 누구든지 RISC-V 칩과 소프트웨어를 설계, 제조, 판매할 수 있게 허가되어 있다. 최초의 개방형 ISA는 아니지만 웨어하우스 규모의 클라우드 컴퓨터, 고성능 휴대 전화, 초소형 임베디드 시스템에 이르는 현대의 산술 장치에 유용하게 쓰일 수 있게 설계되어 있다. 이러한 이용에 근거하여 설계자들은 성능과 전력 효율성을 둘 다 고려하였다. 명령어 집합은 또한 지원 소프트웨어의 실질적인 부분을 포함하고 있어서 새로운 명령어 집합의 일반적인 약점을 보완한다.

2010년 UC 버클리의 컴퓨터과학 연구원들에 의해 RISC-V가 결성됐다. UC 버클리의 컴퓨터과학과는 1980년대에도 MIPS 컴퓨터 구조의 기반이 된 Berkeley RISC 컴퓨터 구조를 성공시킨 바있고 유명한 컴퓨터과학자 데이비드 패터슨 교수도 프로젝트에 참여했다.

이 프로젝트는 캘리포니아 대학교 버클리에서 2010년에 시작되었으나 수많은 기여자들은 자발적인 봉사자들이자 대학 밖의 산업 노동자들이다.[1]

RISC-V ISA는 실생활의 소형, 고속, 저전력 구현체를 염두에 두고 설계되었으나,[2][3] 특정 마이크로아키텍처 스타일을 따르지는 않았다.[3][4][5][6]

2017년 5월 기준으로 버전 2.2의 유저스페이스 ISA가 픽스되어 있으며 privileged ISA는 초안판 1.10으로 이용이 가능하다.[3]

중요성

편집RISC-V의 개발자들은 BSD 허가서 하에서 자유롭게 사용할 수 있는 여러 CPU 디자인을 제공하는 것을 목표로 하였다. 이러한 라이선스들은 RISC-V 칩 디자인과 같은 파생작들이 RISC-V 그 자체와 비슷하게 오픈·자유를 따르거나, 클로즈드·사유를 따를 수 있게 하고 있다.

이와 반대로, ARM 홀딩스와 MIPS 테크놀로지스와 같은 상업적인 칩 벤더들은 자신들의 특허 사용에 대한 상당한 라이선스 비용을 부과한다.[7] 이들은 또한 설계적 장점과 명령어 집합을 기술하는 문서를 출시하기 전에 비공개 계약(NDA)을 요구한다. 수많은 설계적 개선사항들이 완전히 사유이며, 심지어는 고객을 대상으로 설명하지 않는다. 이러한 기밀은 공공의 교육적인 이용, 보안 감사, 공공의 낮은 비용의 자유-오픈 소스 소프트웨어 컴파일러, 운영 체제의 개발을 막아버린다.

CPU를 개발하는 것은 여러 전문분야의 설계적 전문 지식이 필요하다: 전자 논리, 컴파일러, 운영 체제. 전문 엔지니어링 팀 밖에서는 이러한 정보를 찾기가 어렵다. 그 결과로 현대의 고품질의 범용 목적의 컴퓨터 명령어 집합들이 최근까지도 학술적 환경을 제외하고는 어디에서도 사용할 수도 없고 설명되지도 않았다. 이러한 이유로 수많은 RISC-V 기여자들은 이를 통합된 공동체의 노고로 간주한다. 수많은 기여자들의 이러한 요구는 RISC-V가 수많은 용도에 맞게 엔지니어링된 이유 중 하나이다.

RISC-V 개발자들은 또한 실리콘과 시뮬레이션의 설계를 검증하는 것에서 실질적인 연구 및 사용자 경험을 갖추고 있다. RISC-V ISA는 일련의 학술적 컴퓨터 설계 프로젝트의 직접적인 개발품이다. 부분적으로는 이러한 프로젝트들을 지원하기 위해 시작되었다.[3][8]

중국으로의 수출 규제

편집역사

편집선구자

편집"RISC"라는 용어는 약 1980년으로 거슬러 올라간다.[10] 이 이전에 더 단순한 컴퓨터가 더 효율적이라는 이야기는 있었지만 설계적 원칙은 널리 설명되지 않은 상태였다. 단순한 효율적인 컴퓨터는 늘 학술적 관심의 대상이 되고 있다.

여러 학교들에서 1990년에 Computer Architecture: A Quantitative Approach의 제1판을 위해 RISC 명령어 집합 DLX를 개발하였다. 데이비드 패터슨이 저자였으며 나중에 RISC-V를 지원하였다. 그러나 DLX는 교육용이었다. 학계와 취미연구가들은 FPGA를 사용하여 이를 구현하였으나 상업적인 성공을 이루지는 못했다.

버전 2 이하의 ARM CPU들은 퍼블릭 도메인의 명령어 집합을 갖추었으며 인기있는 자유 소프트웨어 컴파일러의 하나인 GCC에 의해 지금도 지원된다. 이로써 ARM 아키텍처의 수용을 가속화시켰다. 3개의 오픈 소스 코어가 이 ISA를 위해 존재하지만 제조된 적은 없다.[11][12]

OpenRISC는 DLX 기반의 오픈 소스 ISA이며, RISC 디자인을 따른다. GCC와 리눅스 구현체를 완전히 지원한다. 그러나 일부 상용 구현체가 존재한다.

재단

편집버클리의 캘리포니아 대학교 Krste Asanović는 오픈 소스 컴퓨터 시스템의 여러 가지 이용을 발견하였다. 2010년에 그는 여름 동안 짧은 3개월 프로젝트에서 개발 및 출판을 결심하였다. 이러한 계획은 학술 부문과 산업 부문의사용자들을 둘 다 지원하기 위한 것이다.[8] 버클리의 데이비드 패터슨은 또한 이 노고를 도왔다. 패터슨은 처음에 버클리 RISC의 속성들을 식별하였으며,[10] RISC-V는 기나긴 일련의 협업 RISC 연구 프로젝트들 가운데 하나이다. 초기 자금 제공은 DARPA에 의해 이루어졌다.[3]

RISC-V 재단을 지원하는 단체들로는 이를테면 다음과 같다: 구글, 마이크로소프트, 엔비디아, 오라클, 퀄컴, IBM, 화웨이, 휴렛 팩커드 엔터프라이즈 (HPE), 인도 공과대학교 마드라스, 어드밴스트 마이크로 디바이시스, BAE 시스템스, Berkeley Architecture Research, Bluespec, Inc., Cortus, Draper, ICT, 래티스 세미컨덕터, Mellanox Technologies, Microsemi, 마이크론, NXP반도체, Rambus Cryptography Research, 웨스턴 디지털, 삼성전자.[13][14]

수상

편집- 2017: The Linley Group's Analyst's Choice Award for Best Technology (명령어 집합에 대해)

설계

편집명령어 하위 집합

편집RISC-V 명령어 중 최소한의 필수적인 집합은 정수 명령어 집합이다. (문자 "I"로 표시) 이 집합은 자체적으로 범용 컴파일러를 포함하여 완전한 소프트웨어 지원과 더불어 단순화된 범용 컴퓨터를 구현할 수 있다.[3]

컴퓨터 설계는 추가적인 하위 집합을 추가할 수 있다: 정수 곱하기 및 나누기 (집합 "M"), 실시간 동시성 처리를 위한 원자적 명령어 ( "A"), 배정밀도("D")와 4배 정밀도("Q") 옵션이 있는 IEEE 부동소수점 ("F").[3] "privileged" 명령어 집합은 유닉스 계열 운영 체제의 지원을 위한 명령어들을 정의한다. 가상화 지원을 위해 하이퍼바이저를 지원할 예정이다.[15] 이러한 명령어 집합 "RVIMAFD"을 갖춘 컴퓨터를 "범용"(general-purpose)이라 부르며 간단히 "G"로 축약한다.[3]

코드 크기(집합 "C")를 줄이는 선택적인 "compact" 하위 집합이 있다. 수많은 RISC-V 컴퓨터들은 이 ISA를 추가하여 전력, 코드 크기, 메모리를 줄일 수 있다.[3] 16개의 레지스터만 지원하여 가장 작은 CPU들에 대한 비용을 줄이는 32비트 임베디드 하위 집합("E")도 있다.[3]

이러한 집합들은 32비트, 64비트와 같은 레지스터의 크기에 따라 추가적으로 기술된다. 각기 다른 레지스터 크기에 대한 각각의 하위 집합의 차이는 크지 않다.

임베디드 시스템용 소형 32비트 컴퓨터는 "RV32EC"일 수 있다. 대형 64비트 컴퓨터는 "RV64G"일 수 있다.[3]

하위 집합은 128비트 컴퓨터, 비트 조작("B"), 10진 부동소수점("L"), Packed SIMD(예: budget multimedia, "P"), 벡터 처리("V"), 트랜잭셔널 메모리("T")도 계획되어 있다.[3]

제품

편집퀄컴은 그동안 ARM 기반 시스템온칩(SoC)을 생산하였으나, 2023년 구글 웨어 OS용 웨어러블 기기의 RISC-V SoC를 개발했다.[16]

같이 보기

편집각주

편집- ↑ “Contributors”. 《riscv.org》. Regents of the University of California. 2018년 6월 13일에 원본 문서에서 보존된 문서. 2014년 8월 25일에 확인함.

- ↑ “Rocket Core Generator”. 《RISC-V》. Regents of the University of California. 2016년 1월 23일에 원본 문서에서 보존된 문서. 2014년 10월 1일에 확인함.

- ↑ 가 나 다 라 마 바 사 아 자 차 카 타 Waterman, Andrew; Asanović, Krste. “The RISC-V Instruction Set Manual, Volume I: Base User-Level ISA version 2.2”. University of California, Berkeley. EECS-2016-118. 2017년 5월 25일에 확인함.

- ↑ Celio, Christopher; Love, Eric. “ucb-bar/riscv-sodor”. 《GitHub Inc.》. Regents of the University of California. 2015년 2월 12일에 확인함.

- ↑ “SHAKTI Processor Project”. Indian Institute of Technology Madras. 2017년 8월 21일에 원본 문서에서 보존된 문서. 2014년 9월 15일에 확인함.

- ↑ Celio, Christopher. “CS 152 Laboratory Exercise 3” (PDF). 《UC Berkeley》. Regents of the University of California. 2015년 2월 12일에 확인함.

- ↑ Demerjian, C. (2013). “A long look at how ARM licenses chips: Part 1”. SemiAccurate.“How ARM licenses it’s IP for production: Part 2”.

- ↑ 가 나 Asanovic, Krste. “Instruction Sets Should be Free” (PDF). 《U.C. Berkeley Technical Reports》. Regents of the University of California. 2016년 11월 15일에 확인함.

- ↑ "오픈소스 동맹도 싹 잘라라"…미중 갈등, ARM 대항마 RISC-V에도 불똥, 2023.10.09, 서울경제, https://sedaily.com/NewsView/29VW4MWRIF

- ↑ 가 나 Patterson, David A; Ditzel, David R. (October 1980). “The Case for the Reduced Instruction Set Computer”. 《ACM SIGARCH Computer Architecture News》 8 (6): 25. doi:10.1145/641914.641917.

- ↑ “Amber ARM-compatible core”. 《OpenCores》. OpenCores. 2014년 8월 26일에 확인함.

- ↑ “ARM4U”. 《OpenCores》. OpenCores. 2014년 8월 26일에 확인함.

- ↑ Merritt, Rick. “Google, Oracle and HP Join RISC-V”. 《EE Times》. UBM. 2017년 8월 24일에 원본 문서에서 보존된 문서. 2016년 2월 11일에 확인함.

- ↑ “보관된 사본”. 2017년 8월 24일에 원본 문서에서 보존된 문서. 2017년 8월 24일에 확인함.

- ↑ Waterman, Andrew; Lee, Yunsup; Avizienas, Rimas; Patterson, David; Asanovic, Krste. “Draft Privileged ISA Specification 1.9”. 《RISC-V》. RISC-V Foundation. 2018년 8월 26일에 원본 문서에서 보존된 문서. 2016년 8월 30일에 확인함.

- ↑ 퀄컴, ARM 의존도 낮춘다…‘RISC-V 웨어러블 플랫폼’ 개발, 2023.10.18, https://www.thelec.kr/news/articleView.html?idxno=23529

추가 문헌

편집- The RISC-V Instruction Set Manual

- Instruction Sets Should Be Free: The Case For RISC-V Whitepaper by Krste Asanović and David A. Patterson

- The RISC-V Instruction Set Archived 2017년 5월 6일 - 웨이백 머신 HotChips 25 (2013)

- The RISC-V Software Ecosystem HPCA 2015, Tutorial

- Rocket Chip HPCA 2015, Tutorial

- The RISC-V Compressed Instruction Set Manual Version 1.9 (draft)

외부 링크

편집- RISC-V - 공식 웹사이트

- (영어) UCB's site for RISC-V - 깃허브

- “RISC-V: An Open Standard for SoCs. The case for an open ISA”. EETimes. 2014년 7월 8일. 2017년 8월 24일에 원본 문서에서 보존된 문서. 2017년 8월 24일에 확인함.

- Pulpino: A developed, open-source system-on-chip based on RISC-V, 4 August 2016

- Hruska, Joel (2014년 8월 21일). “RISC rides again: New RISC-V architecture hopes to battle ARM and x86 by being totally open source”. ExtremeTech.

- “Analyzing the RISC-V Instruction Set Architecture”. en:Adapteva. 2014년 8월 11일.

- RISC-V의 채널 - 유튜브

- “search: RISC-V since 2013”. 《Google Scholar》.